Support for 3DXPoint DIMMs and up-to 2933MHz Ram

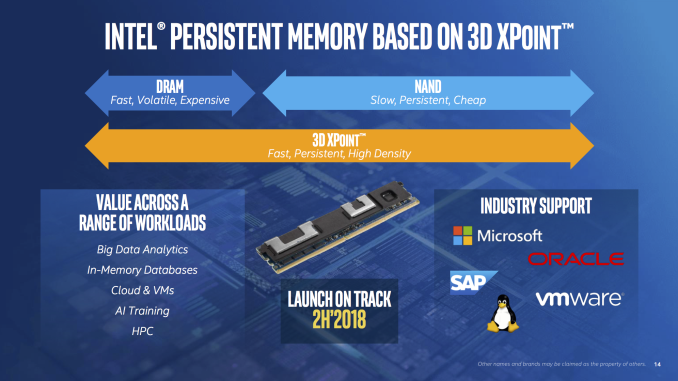

One of the first details I had noticed is the support for Intel's Apache Pass (3DXPoint DIMMs), these have been a long time coming and were originally meant to launch with Skylake SP and the Purley Platform, but instead they will launch with the Purley Platform refresh, Cascade Lake. Apache Pass are Non Volatile DIMMs that go into regular DDR4 slots, these are useful for Big Data Analytics, In-Memory Databases, HPC, Cloud and VMS, etc.

Another detail revealed is higher memory frequency support, from 2666MHz max on Skylake SP to 2993MHz max on Cascade Lake SP, while both provide 6 memory channels Cascade Lake SP will be able to provide a meaningful memory bandwidth increase over Skylake SP.

Multi Chip Package with Integrated FPGA.

This slide tells us about Cascade Lake processors with integrated Arria 10 FPGAs, FPGAs can be used for a plethora of things, like accelerating databases. After Intel's acquisition of Altera in 2015 they have really only now started to leverage Intel's own clout with OEMs such as Dell to spur adoption for FPGAs. They did this by getting server rack vendors to provide FPGAs as alternatives to GPUs. Bringing this back to Cascade Lake, CPU Processors with FPGAs integrated will only further the adoption of FPGAs in the industry and make them much more mainstream, increasing Intel's revenue and market-share in FGPAs. An example of what an CPU Multi Chip Package(MCP) with an integrated FPGA would look like is shown below.

Architectural and Frequency Improvements

"Architectural improvements" can mean lots of things, for example they may have tuned the caches or mesh or perhaps the have tuned the core/uncore itself. Leaks in the past seem to point to the addition of a new AVX512 extension which is named "AVX512_VNNI"(Vector Neural Network Instruction) which is used to speed up certain artificial intelligence workloads. Frequency improvements are a given considering Cascade Lake SP is moving to a more mature and higher clocking version of Intel's 14nm process dubbed "14nm++" in comparison Skylake SP is on "14nm+". I suspect both core and mesh will get a clock bump to improve overall performance.

Cascade Lake SP is decent, but boring.

Cascade Lake SP seems like a decent refresh, don't get me wrong but it leaves me wanting more. I would prefer to see more cores, more memory channels, more PCIe Lanes and I/O. I would also much prefer that this was on Intel's fabled 10nm process node that has been delayed time and time again, but alas this is what we get. More Clocks, More FPGAs and More DIMMs. Expected, yet boring. Every other second generation server CPUs on a platform usually was on a smaller node, however Cascade Lake is an exception and I expect this trend to continue with future generations which will be sad to see.

Comments

Post a Comment